# **BIS L-6026 EtherNet/IP**

Technical Description, User's Manual

english

www.balluff.com

| 1 | User Notes                                        | 4  |

|---|---------------------------------------------------|----|

|   | 1.1 About this Manual                             | 4  |

|   | 1.2 Manual layout                                 | 4  |

|   | 1.3 Conventions                                   | 4  |

|   | 1.4 Symbols                                       | 4  |

|   | 1.5 Abbreviations                                 | 5  |

| 2 | Safety                                            | 6  |

|   | 2.1 Intended use                                  | 6  |

|   | 2.2 General notes on device safety                | 6  |

|   | 2.3 Meaning of the warning notes                  | 6  |

| 3 | Getting Started                                   | 7  |

| 4 | Basic Knowledge                                   | 10 |

|   | 4.1 Identification system principles of operation | 10 |

|   | 4.2 Product description                           | 10 |

|   | 4.3 Control function                              | 10 |

|   | 4.4 Data integrity                                | 10 |

|   | 4.5 Bus connection                                | 11 |

| 5 | Technical Data                                    | 12 |

| 6 | Installation                                      | 14 |

|   | 6.1 Processor installation                        | 14 |

|   | 6.2 Interface information/Connection diagrams     | 14 |

|   | 6.3 Changing the EEPROM                           | 15 |

| 7 | Bus Connection                                    | 16 |

|   | 7.1 IP address                                    | 16 |

|   | 7.2 AnyBus IPconfig                               | 16 |

| 8 | Parameterizing the Processor                      | 18 |

|   | 8.1 Basic knowledge                               | 18 |

|   | 8.2 Parameterizing                                | 20 |

| 9 | Device Function                                   | 26 |

|   | 9.1 Function principle BIS L-6026                 | 26 |

|   | 9.2 Function indicators                           | 33 |

|   | 9.3 Examples                                      | 35 |

|   | Appendix                                          | 46 |

User Notes

| 1.1 | About this<br>Manual | This manual describes the processor for the BIS L-6026 identification system and guides you through startup for immediate operation.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-----|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.2 | Manual layout        | The manual is designed so that each section builds on the previous sections.<br>chapter 2: Basic information regarding safety.<br>chapter 3: The main steps in installing the identification system.<br>chapter 4: An introduction into the material.<br>chapter 5: Technical data for the processor.<br>chapter 6: Mechanical and electrical connections.<br>chapter 7: Logging the processor on to the network.<br>chapter 8: User-defined settings for the processor.<br>chapter 9: How the processor and host system work. |  |  |

| 1.3 | Conventions          | The following conventions are used in this manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|     | Enumerations         | Enumerations are represented as a list with bullet points.<br>– Entry 1,<br>– Entry 2.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|     | Actions              | <ul> <li>Action instructions are indicated by a preceding triangle. The result of an action is indicated by an arrow.</li> <li>► Action instruction 1.</li> <li>⇒ Result of action.</li> <li>► Action instruction 2.</li> </ul>                                                                                                                                                                                                                                                                                                |  |  |

|     | Notation             | <ul> <li>Numbers:</li> <li>Decimal numbers are represented without additional description (e.g. 123),</li> <li>hexadecimal numbers are represented by appending the abbreviation hex (e.g. 00hex).</li> </ul> Parameters: Decimal numbers in italian is italian in a gray (ODO 10)                                                                                                                                                                                                                                             |  |  |

|     |                      | Parameters are written in italics, e.g. <i>(CRC_16)</i> .<br><b>Directory paths:</b><br>Paths in which data are or will be saved/stored are represented in small caps<br>(e.g. PROJECT:\DATA TYPES\USERDEFINED).                                                                                                                                                                                                                                                                                                               |  |  |

|     | Cross-references     | Cross-references indicate where additional information on the topic can be found (see "Technical Data" starting page 12).                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 1.4 | Symbols              | Attention!<br>This symbol indicates a safety advisory which must be observed.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|     |                      | Note, tip<br>This symbol indicates general notes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

# User Notes

| BISBalluff Identification SystemCIPCommon Industrial ProtocolCRCCyclic Redundancy CodeDHCPDynamic Host Configuration ProtocolEDSElectronic Data SheetEEPROMElectrical Erasable and Programmable RedEMVElectromagnetic CompatibilityMAC-IDMedia Access Control IdentifierODVAOpen DeviceNet Vendor AssociationPCPersonal ComputerRPIRequested Packed IntervalPLCProgrammable Logic Controller | OM |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

# BIS L-6026 EtherNet/IP Processor

2 Safety

| 2.1 | Intended use                      | The BIS L-6026 processor is a component of the BIS L identification system. Within the identi-<br>fication system it is used for linking to a host computer (PLC, PC).<br>It is intended only for use only in this way and in an industrial environment complying with Class<br>A of the EMC Law.<br>This description applies to processors in series BIS L-6026-034                                                                                                                                                                              |

|-----|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2 | General notes on<br>device safety | <b>Installation and startup</b><br>Installation and startup are to be carried out only by trained specialists. The manufacturer revokes the right to any warranty or liability claims resulting from unauthorized modifications or improper use. When connecting the processor to an external controller, be sure to observe proper polarity for all connections including the power supply (see section "Installation" on page 14). The processor must be operated only using approved power supplies (see section "Technical Data" on page 12). |

|     |                                   | <b>Operation and testing</b><br>It is the responsibility of the operator to ensure that the locally applicable safety regulations are maintained.<br>In case of defects and faults in the identification system which cannot be remedied, take it out of operation and predect against unauthorized use.                                                                                                                                                                                                                                          |

| 2.3 | Meaning of the warning notes      | Attention!<br>The pictogram used with the word "Attention" warns of a possibly hazardous situation for the health of persons or equipment damage.                                                                                                                                                                                                                                                                                                                                                                                                 |

Disregarding these warnings may result in personal injury or equipment damage.Always observe the instructions given for avoiding this hazard.

**Getting Started**

R

Mechanical connection

Fig. 1: Mechanical connection

► Attach processor using (4) M4 screws.

Electrical connection

# 1 Note

Route the ground wire to ground either directly or through an RC combination, depending on the system. When connecting to the Ethernet, be sure that the connector shield is perfectly

connecting to the Ethernet, be sure that the connector shield is perfectly connected to the connector body.

Do not alter the factory setting for the DIL schwitches.

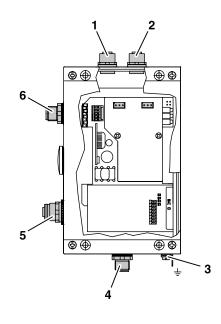

Fig. 2: Electrical connection

- 1 Head 2 Read/write head 2

- 2 Head 1 Read/write head 1

- 3 Function ground FE

- 4 X4 Service port

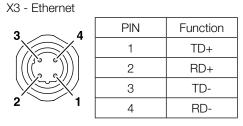

- 5 X3 Ethernet

- 6 X1 Power supply

### Getting Started

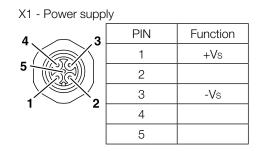

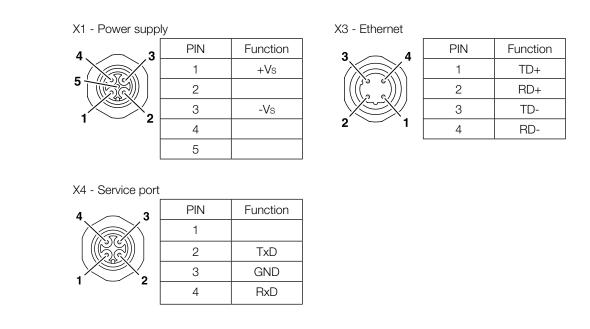

X4 - Service port

| 4 _ 3 | PIN | Function |

|-------|-----|----------|

|       | 1   |          |

|       | 2   | TxD      |

|       | 3   | GND      |

| 1 – 2 | 4   | RxD      |

**Bus connection**

There are two ways of making the bus connection:

- Setting the IP address, subnet mask, gateway address and selecting DHCP using the application "Anybus IPconfig" on a Windows PC having an Ethernet network card.

- Using a DHCP server or BOOTP software.

Use the "Anybus IPconfig" program to make the bus connection. The "Anybus IPconfig" application is included on the BIS SD which comes with the processor.

- ► Start "Anybus IPconfig".

- ⇒ The subnet is scanned for a connected BIS \_-6026. The result of the scan is displayed in the "Anybus IPconfig" window.

| IP Z          | SN            | GW             | DHCP | Version | Туре     | MAC               |

|---------------|---------------|----------------|------|---------|----------|-------------------|

| 169.254.22.54 | 255.255.255.0 | 169.254.22.254 | OH   | 1.04.1  | ABIC-EIP | 00-30-11-02-2F-40 |

|               |               |                |      |         |          |                   |

► Select the device from the scan list and double-click on it.

3 Getting Started

| 🖗 Configure: 00-3  | 30-11-02-2F-40       | 2               |

|--------------------|----------------------|-----------------|

| Ethernet configura | ation                |                 |

| IP address:        | 169 . 254 . 22 . 54  | DHCP            |

| Subnet mask:       | 255 . 255 . 255 . 0  | C On            |

| Default gateway:   | 169 . 254 . 22 . 254 |                 |

| Primary DNS:       | · · · ·              |                 |

| Secondary DNS:     | · · · ·              |                 |

| Hostname:          |                      |                 |

| Password:          |                      | Change password |

| New password:      |                      |                 |

|                    |                      | Set Cancel      |

- Assign the IP address, subnet mask and gateway address.Turn DHCP on/off.

- Confirm your settings by clicking on Set.

# Basic Knowledge

| 4.1 | Identification<br>system principles<br>of operation | The BIS L identification system belongs to the category of non-contact systems having a read and write function. This enables you to not only read data contained in the data carriers, but also to write new data to them at any point in the process.                                                                                                                                                                                                                                 |

|-----|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                     | <ul> <li>The main components of the BIS L identification system are:</li> <li>Processor,</li> <li>read/write heads,</li> <li>data carriers.</li> </ul>                                                                                                                                                                                                                                                                                                                                  |

|     |                                                     | <ul> <li>The main areas of application are:</li> <li>In production for controlling material flow (e.g. for variant-specific processes, workpiece transport using conveying systems, for collecting safety-related data),</li> <li>in inventory systems for monitoring inventory movements,</li> <li>in transport and conveying technology.</li> </ul>                                                                                                                                   |

| 4.2 | Product<br>description                              | <ul> <li>BIS L-6026 processor:</li> <li>Metal enclosure,</li> <li>round connectors for making plug connections,</li> <li>capacity for two read/write heads,</li> <li>read/write heads are suitable for both dynamic and static operation,</li> <li>processor provides power for system components,</li> <li>Carrier signal from the read/write heads provides power for the data carrier.</li> </ul>                                                                                    |

| 4.3 | Control function                                    | The processor represents the link between the data carrier and the host control system.<br>It manages two-way data transfer between the data carrier and read/write head and provides<br>a buffer storage function. The processor writes data from the host signal to the data carrier<br>through the read/write head, or reads data from the data carrier and makes the data available<br>to the host system.                                                                          |

|     |                                                     | Host systems may be:<br>– A control computer (e.g. industrial PC),<br>– a PLC.                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |                                                     | <b>Dual bit-header:</b><br>In order to ensure consistency of the transmitted data, the control bits in the first and last byte (bit-header) of the data buffer for each read/write head are sent and compared. If the two bit-headers are identical, then the data were fully updated and may be accepted. This means that the data for each read/write head are only valid if both bit-headers are identical. The host system must therefore also compare the bits in the bit-headers. |

| 4.4 | Data integrity                                      | To ensure data integrity the data transfer between data carrier and processor must be monitored using a check procedure. The factory default setting in the processor is for double read with compare. A CRC_16 check may however be selected as an alternative. In CRC_16 checking a check code is written to the data carrier, which enables checking the data for validity at any time. Which procedure is used depends on how you are using the identification system.              |

|     |                                                     | Note<br>Mixed operation of the two check procedures is not possible!                                                                                                                                                                                                                                                                                                                                                                                                                    |

Basic Knowledge

The following table provides an overview of the advantages of each respective check procedure.

| CRC_16 data check                                                                           | Double read                                           |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Data integrity even during the non-active phase (data carrier outside the read/write head). | No user data bytes are lost for storing a check code. |

| Shorter read time – page is read just once.                                                 | Shorter read time – no check code is written.         |

#### **4.5 Bus connection** The processor and host system communicate using EtherNet/IP protocol.

EtherNet/IP is an industrial network standard. The IP in EtherNet/IP stands for "Industrial Protocol". EtherNet/IP uses the open communications protocol "Common Industrial Protocol" (CIP) on the application layer (as per the ISO/OSI reference model). EtherNet/IP is supported by the network organization "Open DeviceNet Vendor Association".

Use of a switch in full-duplex mode is necessary for collision-free data exchange.

# 5 Technical Data

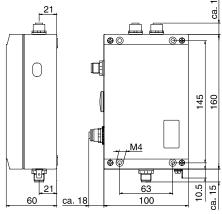

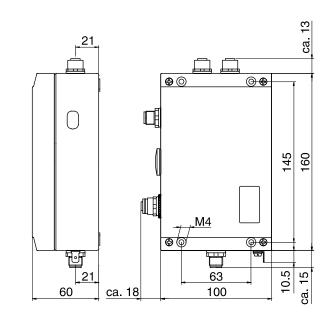

### Dimensions

Fig. 3: Dimensions in mm

#### Mechanical data

| Housing material                        | EN AC-AISi12 (a), DIN EN 1706          |

|-----------------------------------------|----------------------------------------|

| X1 – Input                              | V <sub>s</sub> 24 VDC – 5-pin terminal |

| X3 – Ethernet                           | M12 – 4-pin socket, D-coded            |

| X4 – Service port                       | RS 232 – 4-pin terminal                |

| Head 1, 2 (Write/read head connections) | 8-pin socket                           |

| Enclosure rating                        | IP65 (with plugs connected)            |

| Weight                                  | 950 g                                  |

#### **Electrical data**

| Operating voltage $V_s$ | 24 V DC ±10 % |

|-------------------------|---------------|

| Ripple                  | ≤ 10 %        |

| Current consumption     | ≤ 400 mA      |

| Device interface        | Ethernet      |

| Service port            | RS 232        |

# **5** Technical Data

Operating conditions

| Ambient temperature                  | 0 °C 60 °C                                                           |

|--------------------------------------|----------------------------------------------------------------------|

| EMV                                  |                                                                      |

| – EN 61000-4-2/3/4/5/6<br>– EN 55011 | <ul><li>Severity level 4A/3A/4A/1A/3A</li><li>Gr. 1, Cl. A</li></ul> |

| Shock/Vibration                      | EN 60068 Part 2-6/27/29/64/32                                        |

Function indicators

| BIS operating states | Ready<br>CT1 Present/Operating<br>CT2 Present/Operating                            | Green LED<br>Green/yellow LED<br>Green/yellow LED |

|----------------------|------------------------------------------------------------------------------------|---------------------------------------------------|

| Status EtherNet/IP   | Data Rate (DR)<br>Module Status (MS)<br>Network Status (NS)<br>Link/Activity (L/A) | LED<br>LED<br>LED<br>LED                          |

# BIS L-6026 EtherNet/IP Processor

**installation**

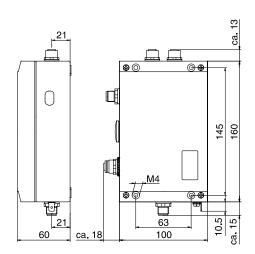

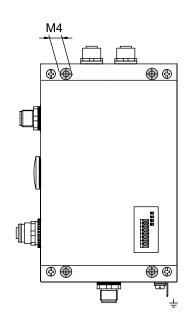

6.1 Processor installation

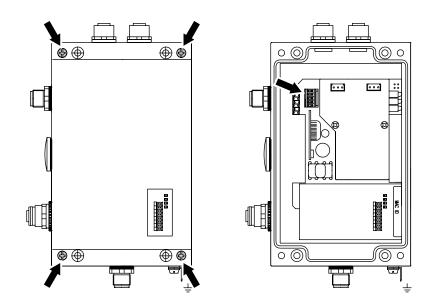

Fig. 4: Installation

► Attach processor using (4) M4 screws.

# i Note

Route the ground wire to ground either directly or through an RC combination, depending on the system. When connecting to the Ethernet, be sure that the connector shield is perfectly

when connecting to the Ethernet, be sure that the connector shield is perfectly connected to the connector body.

Do not alter the factory setting for the DIL switches.

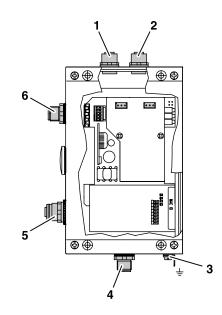

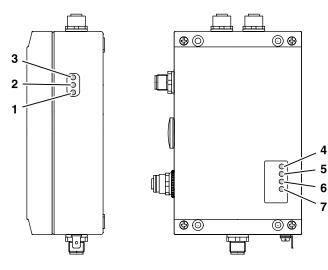

Fig. 5: Processor connections

- 1 Head 2 Read/write head 2

- 2 Head 1 Read/write head 1

- 3 Function ground FE

- 4 X4 Service port

- 5 X3 Ethernet

- 6 X1 Power supply

**installation**

6.3 Changing the EEPROM

# Attention!

Components may be damaged by electrostatic discharge.

Be sure to turn off power to the device before opening it.

Fig. 6: Changing the EEPROM

- ► Remove 4 screws from housing cover and remove cover.

- ► Pull EEPROM from socket.

- ► Insert new EEPROM into socket.

- ► Replace cover and tighten 4 screws.

# 7 Bus Connection

| 7.1                 | IP address | The processor and host system communicate using EtherNet/IP protocol. Assigning a unique IP address associates the processor with a network.                                                                                                                                                                                                                                                       |

|---------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |            | The processor can be incorporated into a network in various ways (DHCP, ARP). The MAC address is used as the basis for incorporating into the network. This hardware address is used only one time and uniquely identifies network devices such as the processor.                                                                                                                                  |

|                     | DHCP       | Dynamic Host Configuration Protocol (DHCP) allows a server to be used for dynamic assigning of an IP address. The hardware can be inserted into the network without having to perform any additional configuration. Only automatic obtaining (MAC address) of the IP address needs to be set.                                                                                                      |

| 7.2 AnyBus IPconfig |            | "AnyBus IPconfig" is software which allows the hardware to be addressed for the corresponding<br>subnet prior to installation. In addition, assigning of the IP address through a DHCP server or<br>BOOTP program can be activated (DHCP on) or deactivated (DHCP off).<br>The "Anybus IPconfig" application is included on the BIS SD which comes with the processor.<br>Start "Anybus IPconfig". |

|                     |            | The subnet is scanned for a connected BIS6026. The result of the scan is displayed in the "Anybus IPconfig" window.                                                                                                                                                                                                                                                                                |

|                     |            | 🖝 Anybus IPconfig                                                                                                                                                                                                                                                                                                                                                                                  |

|                     |            |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Allybus IPcollin | y             |                |      |         |          |      |              |        |

|------------------|---------------|----------------|------|---------|----------|------|--------------|--------|

| IP A             | SN            | GW             | DHCP | Version | Туре     |      | MAC          |        |

| 169.254.22.54    | 255.255.255.0 | 169.254.22.254 | Off  | 1.04.1  | ABIC-EIP |      | 00-30-11-02- | -2F-40 |

|                  |               |                |      |         |          |      |              |        |

|                  |               |                |      |         |          |      |              |        |

|                  |               |                |      |         |          |      |              |        |

|                  |               |                |      |         |          |      |              |        |

|                  |               |                |      |         |          |      |              |        |

|                  |               |                |      |         |          |      |              |        |

|                  |               |                |      |         |          |      |              |        |

|                  |               |                |      |         |          |      |              |        |

|                  |               |                |      |         |          |      |              |        |

|                  |               |                |      |         |          |      |              |        |

|                  |               |                |      |         |          | Scan |              | Exit   |

|                  |               |                |      |         |          |      |              |        |

- Select the device from the scan list and double-click on it.

- $\Rightarrow$  The "Configure" window is opened.

#### 7 **Bus Connection**

| Ethernet configura | ition                |                   |

|--------------------|----------------------|-------------------|

| IP address:        | 169 . 254 . 22 . 54  | DHCP              |

| Subnet mask:       | 255 . 255 . 255 . 0  | O On              |

| Subrict mask.      | 200 . 200 . 200 . 0  | Off               |

| Default gateway:   | 169 . 254 . 22 . 254 |                   |

| D. D. D.           |                      |                   |

| Primary DNS:       |                      |                   |

| Secondary DNS:     |                      |                   |

|                    |                      |                   |

| Hostname:          |                      |                   |

| Password:          |                      | 🔲 Change password |

|                    |                      |                   |

| New password:      |                      |                   |

- Assign the IP address, subnet mask and gateway address.

Turn DHCP on/off.

- Confirm your settings by clicking on Set.

#### 8.1 Basic knowledge

Data carrier types

Two data carrier models are available for the BIS L-6026 processor. Depending on your selection either all or only one particular data carrier can be processed.

| Data carrier      | BIS L-1001/L                                                                                                                                   | BIS L-2003/L                                                                                                                                   |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter         |                                                                                                                                                |                                                                                                                                                |  |

| Memory capacity   | 192 bytes of user data (read/write) +<br>4 bytes of fixed serial number (read-<br>only).                                                       | 5 bytes of fixed serial number<br>(read-only), corresponding to the<br>user data.                                                              |  |

| CT Present        | The first user data are read from the data carrier and loaded into the input buffer.<br>If " <i>Output function type and serial num</i> gured: | 5 bytes of the serial number are<br>read from the data carrier and<br>loaded into the input buffer.<br><i>mber when CT present</i> " is confi- |  |

|                   | Output type 01hex in byte 1 of the input buffer and then the 4 bytes of unique serial number.                                                  | Output type 03 <sub>hex</sub> in byte 1 of the input buffer and then the 5 bytes of unique serial number.                                      |  |

| Functions         | The full command set of the<br>BIS L-6026 processor is available.                                                                              | No commands from the<br>BIS L-6026 processor are<br>required (all data are output as<br>soon as CT Present is active).                         |  |

| Device parameters | Depends on the number of bytes to<br>be read/written for each read/write<br>head.                                                              | <i>DTTyp</i> to 'All Tag Types' or<br>'BIS L-20_'<br><i>TypSN</i> to 'Enable'.                                                                 |  |

Type BIS L-10\_-01/L data carriers are shipped configured with FFnex37hex . Only data

carriers having this configuration are processed.

The BIS L-10\_-01/L carrier contains additional memory ranges for configuration and protected data. These ranges cannot be processed using the BIS L-6026 processor.

#### **CRC** check

The CRC check is a procedure for determining a test value for data so as to detect errors in transferring data. If CRC check is activated, an error message is output when a CRC error is detected.

#### Initializing

To be able to use the CRC check, the data carriers must be initialized. The data carriers are initialized in the output buffer using the command 12<sub>hex</sub> If the data carrier does not contain the correct CRC, then the processor sets an error message in the input buffer (see Example 10 on page 44).

As shipped from the factory, data carriers may be immediately written a checksum, since all the data are set to 0.

#### Error message

- If an error message is the result of a failed write job, then the data carrier must be reinitialized before it can be used again.

- If an error message is not the result of a failed write job, then one or more of the memory cells in the data carrier are defective. This means the data carrier must be replaced.

#### Checksum

The checksum is written to the data carrier as a 2-byte information. 2 bytes per block are lost. This leaves 14 bytes remaining per block. The usable number of bytes can be determined from the following table.

| Data carrier type | Memory capacity | Usable bytes            |

|-------------------|-----------------|-------------------------|

| BIS L-1001/L      | 192 bytes       | 168 bytes               |

| BIS L-2003/L      | 5 bytes         | CRC_16 is not supported |

| Simultaneous            | Reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| data transmission       | The processor reads the data from the data carrier directly into the input buffer. As soon as the buffer is filled, the Toggle-Bit Out (TO-Bit) is inverted to indicate data ready to the host system. The system inverts the Toggle-Bit In (TI-Bit) to indicate that it is ready to receive, and data read in the meantime are transmitted to the input buffer. This repeats itself until the desired data have been read from the data carrier. After the read procedure is finished, the processor sets the Job End bit (AE-bit) and transmits the remaining data to the input buffer (see example 2 on page 36). |

|                         | Writing<br>The processor begins to write data to the data carrier as soon as it has received the first data<br>from the host system. Once all the data have been written to the data carrier, the AE-bit is set.                                                                                                                                                                                                                                                                                                                                                                                                     |

| Dynamic mode            | As soon as the Dynamic function is activated, the processor accepts the read/write job from the host system and stores it regardless of whether there is a data carrier in the active zone of the read/write head. When a data carrier enters the active zone of the read/write head, the stored job is carried out                                                                                                                                                                                                                                                                                                  |

| Auto-Read<br>(Standard) | When a data carrier enters the active zone of the read/write head 14 bytes starting at address $OO_{hex}$ are automatically read into the input buffer. No additional read command is required. This allows small data amounts which are stored starting at address $OO_{hex}$ to be read faster. If a BIS L-2003/L data carrier is in front of the read/write head, a maximum of 5 bytes are sent to the input buffer.                                                                                                                                                                                              |

|                         | If the parameter <i>TypSN</i> (Type and serial number when CT Present) is set, then instead of the user data the data carrier type and the unique serial number of the data carrier are sent. For type BIS L-2003/L this is always the serial number.                                                                                                                                                                                                                                                                                                                                                                |

|     | Auto-Read Extra        | If Auto-Read <i>Extra</i> is activated, then the 14 bytes starting at a specified address are read from the data carrier to the input buffer and then the Codetag Present bit (CP bit) is set. The start address is specified using the parameter <i>Extra_Adr</i> .                                                                                                                                                                                                                                      |                                   |                                                                                                                       |  |  |

|-----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

|     |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   | version V2.0 and higher the number of bytes to read sing the parameter <i>CP_Number</i> .                             |  |  |

|     | Type and serial number |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | issued. For the                   | nt the data carrier type and serial number (UID = unique data carrier type BIS M-1 $\_$ -02/L this is a useful appli- |  |  |

| 8.2 | Parameterizing         | There are two different w using the EDS file.                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ays to set param                  | eters. Parameterizing from an application program or                                                                  |  |  |

|     | Basics                 | The parameters for operating the processor are stored in the BIS Sonfig Object (class 6 Explicit messages are used to access the parameters.                                                                                                                                                                                                                                                                                                                                                              |                                   |                                                                                                                       |  |  |

|     |                        | <ul> <li>Parameterizing from an application program</li> <li>One widely used application for EtherNet/IP device parameterizing is the Wind RSLogix 5000 written for the Logix 5000 controller of Rockwell Automation. And device programming is included on the BIS-CD. For additional information see "Example for parameterizing with application program" on page 21.</li> <li>EDS file</li> <li>The EDS file contains all the device parameters for the processor. The file is ind BIS-CD.</li> </ul> |                                   |                                                                                                                       |  |  |

|     | Parameters             | CRC_16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | class:<br>instance:<br>attribute: | 64hex<br>01hex<br>01hex                                                                                               |  |  |

|     |                        | Factory setting:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Disable                           | (= 0)                                                                                                                 |  |  |

|     |                        | Data validity is checked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | using double rea                  | ad.                                                                                                                   |  |  |

|     |                        | Other settings:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Enable                            | (= 1)                                                                                                                 |  |  |

|     |                        | Data validity is ensured                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | using CRC chec                    | κ.                                                                                                                    |  |  |

|     |                        | Simultaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | class:<br>instance:<br>attribute: | 64hex<br>01hex<br>02hex                                                                                               |  |  |

|     |                        | Factory setting:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Disable                           | (= 0)                                                                                                                 |  |  |

|     |                        | Read/write jobs and dat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ta transmission a                 | re run in sequence.                                                                                                   |  |  |

|     |                        | Other settings:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Enable                            | (= 1)                                                                                                                 |  |  |

|     |                        | Read/write jobs and dat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ta transmission a                 | re run simultaneously.                                                                                                |  |  |

| Dynamic1                    | class:                            | 64hex                                                                               |

|-----------------------------|-----------------------------------|-------------------------------------------------------------------------------------|

|                             | instance:<br>attribute:           | O1hex<br>O3hex                                                                      |

| Factory setting:            | Disable                           | (= 0)                                                                               |

|                             | tatic mode. Re                    | ad/write command from the controller is carried out                                 |

|                             |                                   | e zone of Read/Write Head 1.                                                        |

| Other settings:             | Enable                            | (= 1)                                                                               |

| Read/Write Head 1 is in c   | lynamic mode.                     |                                                                                     |

| Dynamic2                    | class:                            | 64hex                                                                               |

|                             | instance:<br>attribute:           | 01hex<br>04hex                                                                      |

| Factory setting:            | Disable                           | (= 0)                                                                               |

| Read/write head 2 is in st  |                                   | ad/write command from the controller is carried out<br>e zone of Read/Write Head 2. |

| Other settings:             | Enable                            | (= 1)                                                                               |

| Read/Write Head 2 is in c   | dynamic mode.                     |                                                                                     |

| Extra1                      | class:                            | 64hex                                                                               |

|                             | instance:<br>attribute:           | 01hex<br>05hex                                                                      |

| Factory setting:            | Disable                           | (= 0)                                                                               |

|                             | s a data carrier                  | r in the active zone of Read/Write Head 1.                                          |

| Other settings:             | Enable                            | (= 1)                                                                               |

| The Auto-Read function is   | s active.                         |                                                                                     |

| Eutro 0                     |                                   | 04                                                                                  |

| Extra2                      | class:<br>instance:<br>attribute: |                                                                                     |

| Factory setting:            | Disable                           | (= 0)                                                                               |

| CT Present data if there is | s a data carrier                  | r in the active zone of Read/Write Head 2.                                          |

| Other settings:             | Enable                            | (= 1)                                                                               |

| The Auto Deed function i    | e estive                          |                                                                                     |

The Auto-Read function is active.

| Extra_Adr1       | class:<br>instance:<br>attribute: | - |

|------------------|-----------------------------------|---|

| Factory setting: | 0                                 |   |

| Other settings:  | 1191                              |   |

Specifies the start address (Auto-Read) beginning at which the data carrier is read when a data carrier enters the active zone of Read/Write Head 1.

| class:<br>instance:<br>attribute: | -                            |

|-----------------------------------|------------------------------|

| 0                                 |                              |

| 1191                              |                              |

|                                   | instance:<br>attribute:<br>0 |

Specifies the start address (Auto-Read) beginning at which the data carrier is read when a data carrier enters the active zone of Read/Write Head 2.

| TypSN                                                                                     | class:<br>instance:<br>attribute: |       |  |  |

|-------------------------------------------------------------------------------------------|-----------------------------------|-------|--|--|

| Factory setting:                                                                          | Disable                           | (= 0) |  |  |

| At CT Present the data carrier type and the serial number of the data carrier are output. |                                   |       |  |  |

| Other settings:                                                                           | Enable                            | (= 1) |  |  |

| class:<br>instance:<br>attribute: | 64hex<br>01hex<br>0Ahex                                                                                      |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------|

| All data carrier types            | (= 0)                                                                                                        |

| either all or only one part       | ticular data carrier can be processed.                                                                       |

| BIS L-1001/L                      | (= 1)                                                                                                        |

| Not used                          | (= 2)                                                                                                        |

| BIS L-2003/L                      | (= 3)                                                                                                        |

|                                   | instance:<br>attribute:<br>All data carrier types<br>either all or only one part<br>BIS L-1001/L<br>Not used |

| CP_Number1       | class:<br>instance:<br>attribute: | - |

|------------------|-----------------------------------|---|

| Factory setting: | 4                                 |   |

| Other settings:  | 114                               |   |

Specify the number of bytes to be read when a data carrier enters the active zone of read/write head 1.

Only active for hardware version V2.0 and higher of the read/write head. For hardware versions <V2.0 14 bytes are always read.

| CP_Number2       | class:<br>instance:<br>attribute: | - |

|------------------|-----------------------------------|---|

| Factory setting: | 4                                 |   |

| Other settings:  | 114                               |   |

Specify the number of bytes to be read when a data carrier enters the active zone of read/write head 2.

Only active for hardware version V2.0 and higher of the read/write head. For hardware versions < V2.0 14 bytes are always read.

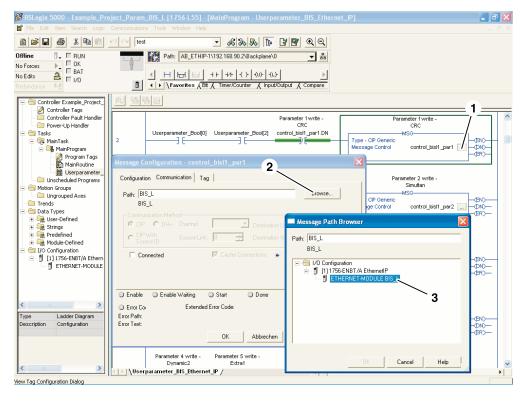

Example of parameterizing using the application program

This example shows how the example project included on the BIS-CD can be used with the RSLogix 5000 software for a user project.

Note the following procedure:

- 1. Add the BIS L-6026 to a user project.

- 2. Import the example project into a new project.

- 3. Copy user-defined data type from the example project to the user project.

- 4. Create a sub-routine in the user project.

- 5. Set invoking of the sub-routine in the main program of the user program.

To run the example the files stored on the BIS-CD must by copied to a local directory.

Note

Information about the software, installation, creating projects and working in projects can be found in the manual for the RSLogix 5000 manual.

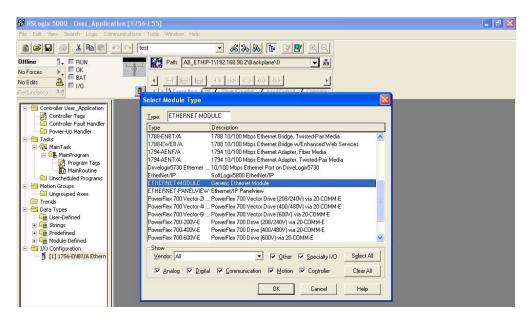

#### 1. Add the processor

- Open user project. ►

- Under I/O-Configuration\[1] 1756-ENBT/A ETHERNETIP create a new module. ► (type: Generic Ethernet Module).

| ► | Set module properties:                        |   |                                    |

|---|-----------------------------------------------|---|------------------------------------|

|   | Name:<br>Communication format:<br>IP address: | 0 | BIS_L<br>Data SINT<br>192.168.90.3 |

#### Set the connection parameters as follows:

|                       |                | Instance | Size     |

|-----------------------|----------------|----------|----------|

| Connection parameters | Input:         | 100      | 32 bytes |

|                       | Output:        | 150      | 32 bytse |

|                       | Configuration: | 1        | 0        |

# i

Note

"Configuration" is not supported. Therefore the values are set to 1 and 0.

| Module Pre                  | operties - EthernetIP (ETHERN                                | VET-MODULE 1.          | 1)                    | 2            |

|-----------------------------|--------------------------------------------------------------|------------------------|-----------------------|--------------|

| General Con                 | nection Module Info                                          |                        |                       |              |

| Type:<br>Vendor:<br>Parent: | ETHERNET-MODULE Generic Ether<br>Allen-Bradley<br>EthernetIP |                        |                       |              |

| Na <u>m</u> e:              | BIS_L                                                        | Connection Par         |                       |              |

| Description:                |                                                              |                        | Assembly<br>Instance: | Size:        |

|                             |                                                              | Input:                 | 100                   | 32 ÷ (8-bit) |

|                             |                                                              | O <u>u</u> tput:       | 150                   | 32 🔹 (8-bit) |

| Comm <u>F</u> ormat         | t Data - SINT 📃                                              | <u>C</u> onfiguration  | 1                     | 0 ÷ (8-bit)  |

| • IP <u>A</u> ddr           |                                                              | <u>S</u> tatus Input:  |                       |              |

| C <u>H</u> ost Na           | ame:                                                         | S <u>t</u> atus Outpul |                       |              |

| Status: Offline             | ОК                                                           | Cancel                 | Apply                 | Help         |

Save settings by clicking on "OK" and confirm the remaining dialog fields until the module has been successfully created.

#### Note

When confirming the dialog fields, be sure that the Requested Packed Interval (RPI)  $\geq$  10 ms is set.

#### 2. Import example project

Only one project per window can be opened in RSLogix 5000.

- ► Open a new project.

- Import the example project "Example\_Project\_Param\_BIS\_L.L5K" from the local directory to the project (File\Open).

- ► Save example project in \*.ACD format (File\Save as) File name is freely selectable.

#### 3. Copy user-defined data type

- ► Under Data Types\User defined in the example project copy "BIS\_L\_Userparameters".

- ► Under Data Types\User defined in the example project paste "BIS\_L\_Userparameters".

#### 4. Create a sub-routine in the user project

- ► Under Tasks\MainTask\MainPRogRam in the user project create a new routing with the name "Userparameters\_BIS\_Ethernet\_IP".

- Double-click to open the new routine.

- ► Right-click on "Import flow path" from the context menu.

- Import the file "Example\_Project\_Rung\_BIS\_L.L5X" from the local directory to the user project.

- ► Reconfigure the communication paths for all messages see screenshot for sequence.

#### 5. Set invoking of the sub-routine

- ► Under Tasks\MainTask\MainProgram select MainRoutine.

- In the MainRoutine set "Userparameter\_Bool (0)" to high.  $\Rightarrow$  Sub-routine is activated.

9.1 Function principle BIS L-6026

Bis L-6026

Two buffers are required to exchange data and commands between the processor and the host system. Cyclical polling is used for exchanging the buffer contents. The buffer content depends on the cycle in which it is written (e.g. control commands at the start of the job). When writing the buffer, the transmitted data from the previous cycle are overwritten. Unwritten bytes are not deleted and retain their data content.

The buffer size of the overall buffer is 32 bytes. 16 bytes are available for each read/write head.

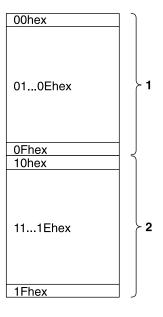

Fig. 7: Total buffer Read/Write Heads 1 and 2

1 Read/Write Head 1

2 Read/Write Head 2

Only 14 bytes per read/write head are available for data exchange, since the first and last bytes in the respective data buffer are used for control and for status messages.

The output buffer is used to transmit the identification system commands and the data to be written to the data carrier.

| Bit no.                           | 7     | 6                                        | 5       | 4 | 3     | 2  | 1  | 0   |

|-----------------------------------|-------|------------------------------------------|---------|---|-------|----|----|-----|

| Subaddress                        |       |                                          |         |   |       |    |    |     |

| 00 <sub>hex</sub> =<br>Bit header |       | TI                                       | KA      |   |       | GR |    | AV  |

| 01hex                             |       |                                          | Commanc |   |       | or | Da | ata |

| 02hex                             | Stare | Stared address (Low Byte) or program no. |         |   | m no. | or | Da | ata |

| 03hex                             |       | Start address (High Byte)                |         |   |       | or | Da | ata |

| 04hex                             |       | No. of bytes (Low Byte)                  |         |   |       | or | Da | ata |

| 05hex                             |       | No. of bytes (High Byte)                 |         |   |       | or | Da | ata |

| 06hex                             | Data  |                                          |         |   |       |    |    |     |

|                                   | Data  |                                          |         |   |       |    |    |     |

| 0F <sub>hex</sub> =<br>Bit header |       | TI                                       | KA      |   |       | GR |    | AV  |

### Output buffer

# Allocation and explanation

| Subaddress  | Bit name  | Meaning       | Function description                                                                                  |

|-------------|-----------|---------------|-------------------------------------------------------------------------------------------------------|

| 00hex/0Fhex | ΤI        | Toggle-Bit In | Controller is ready to receive additional data (read job).                                            |

|             | KA        | Head deselect | Turns the read/write head off.                                                                        |

|             | GR Base s |               | Identification goes into base state for the respective read/write head. Any pending job is cancelled. |

|             | AV        | Job           | A job is pending for the respective read/write head.                                                  |

| Subaddress | Meaning      | Function description                             |

|------------|--------------|--------------------------------------------------|

| 01hex      | Command      |                                                  |

|            | 00hex        | No command.                                      |

|            | 01hex        | Read data carrier.                               |

|            | 02hex        | Write to data carrier.                           |

|            | 06hex        | Save program for                                 |

|            |              | "Mixed data access" in EEPROM.                   |

|            | 12hex        | Initialize CRC_16 data check.                    |

|            | 21hex        | Read data carrier as per a program for           |

|            |              | "Mixed data access".                             |

|            | 22hex        | Write to data carrier as per a program for       |

|            |              | "Mixed data access".                             |

|            | or Data      | Transmitting data written to the data carrier.   |

|            |              |                                                  |

|            | or           | Transmitting program data written to the EEPROM. |

|            | Program data |                                                  |

| 02hex | Start address<br>(Low Byte) | Address starting at which reading or writing should commence (address range from 0 to 191 is covered).                                                                          |

|-------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | or<br>Program No.           | Program No. to be stored for "Mixed Data Access" in conjunction with command 06hex (value range 01hex to 0Ahex).                                                                |

|       | or<br>Program No.           | Program No. to be run for "Mixed Data Access" in con-<br>junction with command 21 <sub>hex</sub> or 22 <sub>hex</sub> (value range 01 <sub>hex</sub><br>to 0A <sub>hex</sub> ). |

|       | or<br>Data                  | Transmitting data written to the data carrier.                                                                                                                                  |

|       | or<br>Program data          | Transmitting program data written to the EEPROM.                                                                                                                                |

| 03hex | Start address<br>(High Byte) | Address starting at which reading or writing should com-<br>mence (at current data carrier capacity always 0). |

|-------|------------------------------|----------------------------------------------------------------------------------------------------------------|

|       | or<br>Data                   | Transmitting data written to the data carrier.                                                                 |

|       | or<br>Program data           | Transmitting program data written to the EEPROM.                                                               |

| Subaddress | Meaning                     | Function description                                                                                               |

|------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------|

| 04hex      | No. of bytes<br>(Low Byte)  | No. of bytes (1 to 192 bytes) to read or write beginning at the start address (Low Byte).                          |

|            | or<br>Data                  | Transmit the data which are written to the data carrier.                                                           |

|            | or<br>Program data          | Transmitting program data written to the EEPROM.                                                                   |

|            |                             |                                                                                                                    |

| 05hex      | No. of bytes<br>(High Byte) | No. of bytes to read or write<br>commencing with the start address (at current data carrier<br>capacity always 0). |

|            | or                          | Transmitting data written to the data carrier.                                                                     |

| or<br>Data         | Transmitting data written to the data carrier.   |

|--------------------|--------------------------------------------------|

| or<br>Program data | Transmitting program data written to the EEPROM. |

| 06hex | Data               | Transmitting the data written to the data carrier.         |

|-------|--------------------|------------------------------------------------------------|

|       | or<br>Program data | Transmit the program data which are written to the EEPROM. |

| <br>Data           | Transmitting the data written to the data carrier.         |

|--------------------|------------------------------------------------------------|

| or<br>Program data | Transmit the program data which are written to the EEPROM. |

### Input buffer

The input buffer is used to transmit the data read by the identification system, the identifiers and error codes to the host system.

| Bit no.<br>Subaddress             | 7                | 6  | 5         | 4   | 3  | 2  | 1  | 0  |

|-----------------------------------|------------------|----|-----------|-----|----|----|----|----|

| 00 <sub>hex</sub> =<br>Bit header | BB               | HF | ТО        |     | AF | AE | AA | CP |

| 01hex                             | D1hex Error code |    | e or Data |     |    |    |    |    |

| 02hex                             | Data             |    |           |     |    |    |    |    |

|                                   |                  |    | Da        | ata |    |    |    |    |

| 0F <sub>hex</sub> =<br>Bit header | BB               | HF | ТО        |     | AF | AE | AA | CP |

# Allocation and explanation

| Subaddress  | Bit name | Meaning         | Function description                                                                                                                         |

|-------------|----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 00hex/0Fhex | BB       | Ready           | Identification system is ready.                                                                                                              |

|             | HF       | Head error      | Cable break on read/write head or no read/<br>write head connected.                                                                          |

|             | то       | Toggle-Bit Out  | Read procedure: Identification system has<br>additional data ready.<br>Write procedure: Identification system can<br>accept additional data. |

|             | AF       | Job error       | Error in processing the job, or job cancelled.                                                                                               |

|             | AE       | Job end         | Confirmation – Job ended without error.                                                                                                      |

|             | AA       | Job start       | Confirmation – Job was recognized and started.                                                                                               |

|             | СР       | Codetag Present | There is a data carrier in the active zone of the read/write head.                                                                           |

| Subaddress | Meaning           | Function description                                                                                               |

|------------|-------------------|--------------------------------------------------------------------------------------------------------------------|

| 01hex      | Error code        | Error number valid only with AF-bit!                                                                               |

|            | 01hex             | Job cannot be carried out becoffe there is no data carrier in the active zone of the read/write head.              |

|            | 02hex             | Read error.                                                                                                        |